# Efficient Realization of Arithmetic Algorithms with Weighted Collections of Posibits and Negabits

# Ghassem Jaberipur<sup>1</sup>

Department of Electrical and Computer Engineering Shahid Beheshti University Tehran 1983963113, Iran

E-mail: jaberipur@sbu.ac.ir

#### Behrooz Parhami

Department of Electrical and Computer Engineering University of California Santa Barbara, CA93106-9560, USA

Phone: +1 805 893 3211, Fax: +1 805 893 3262

E-mail: <a href="mailto:parhami@ece.ucsb.edu">parhami@ece.ucsb.edu</a>

## **Abstract**

The most common uses of negatively weighted bits (negabits), normally assuming the arithmetic value -1 (respectively 0) for logical 1 (0) state, are as the most significant bit of 2's-complement numbers and as the negative component in binary signed-digit (BSD) representation. More recently, weighted bit-set (WBS) encoding of generalized digit sets and the practice of inverted encoding of negabits (IEN) have allowed for easy handling of any equally weighted mix of negabits and ordinary bits (posibits) via standard arithmetic cells, such as half/full adders, bit compressors, and counters. These cells have been highly optimized for a host of simple and composite figures of merit involving delay, power, and area, and they are continually improving due to their wide applicability. In this paper, we aim to promote WBS and IEN as new design concepts for designers of computer arithmetic circuits. We provide a few relevant examples from previously designed logical circuits and redesigns of established circuits such as 2's-complement multipliers and modified booth recoders. Furthermore, we present a modulo- $(2^n + 1)$  multiplier, where the partial products are represented in WBS with IEN. We show that by using standard reduction cells, the partial products can be reduced to two. The result is then converted, in constant time, to BSD representation and, via simple addition, to the final sum. The thoroughly explained process of conversion to BSD is also new.

**Keywords**—(4;2)-compressor, Digit set, Full-adder cell, Inverted encoding of negabits, Parallel compressor, Parallel counter, Redundant number representation, Signed-digit arithmetic, Weighted bit-set encoding,

1

<sup>&</sup>lt;sup>1</sup>G. Jaberipur is also affiliated with School of Computer Science, Inst. for Research in Fundamental Science (IPM).

### 1. Introduction

In the past couple of decades, the computing discipline and its associated products market have been increasingly dominated by media processing and a host of supporting communications and digital signal processing (DSP) applications. The steady rise in the performance of general-purpose and DSP chips has driven not only the market for embedded computing devices, but also influenced the broader scene, from personal computing platforms to supercomputers. Greater technological capabilities and the ever-increasing demand for more functionality in computing and communication devices have driven a tightly-wound cycle of advances that has increased not only the processing speeds, but has done so more economically and at lower energy dissipation. The demand for even greater performance continues to drive the development of hardware for signal processing, to the extent that DSP and graphics chips are now at the leading edge of performance, cost-effectiveness, and energy efficiency.

One way to improve the speed and efficiency of DSP and other arithmetic-intensive applications is through nonstandard number formats. Residue number system (RNS) representations have led the way in this regard since the 1980s [Tayl83], [Sode86], [Omon07]. Redundant number representations [Aviz61], [Parh10] have also been used widely, particularly in reducing the complexity of digital filter implementations via multiplierless designs [Meye07]. Of course, the main strength of redundant representations is in their carry-free addition property, making addition even faster than in RNS. While redundant representations lead to slower multiplication compared with RNS, they can be quite competitive overall, given the elimination of the final carry-propagate addition required in standard weighted representations. Furthermore, elimination of forward (binary to RNS) and reverse (RNS to binary) conversions, and the possibility of multiplierless implementations in some cases can mitigate the speed loss.

One drawback of redundant and other unconventional number representations, as currently used in various applications, is their need for nonstandard hardware building blocks that must be designed from scratch. In this paper, we show how speed can be improved via the introduction and uniform treatment of positively and negatively weighted bits, allowing virtually any

arithmetic algorithm on signed operands (including signed-digit, and other redundant or hybridredundant arithmetic operations) to be performed using the same highly efficient and extensively optimized circuitry used for unsigned values.

Considering the most-significant bit of a 2's-complement number as having a negative weight is a well-known method for simplifying direct signed multiplication [Baug73]. Similarly, negatively weighted bit positions have been used to simplify the interpretation of, and algorithm development for, number systems with negative and imaginary radices [Kore81]. Negatively weighted bits (negabits) have also been used in the  $\langle n, p \rangle$  encoding of binary signed digits [Parh90] and, more recently, in weighted bit-set (WBS) encoding of redundant number systems [Jabe05], signed-LSB representation of modulo- $(2^n\pm 1)$  residues [Jabe09], and signed-digit adders [Jabe10a], [Gorg11], where a combination of weighted encoding of a digit set and a power-of-2 radix allows efficient implementation of arithmetic with redundant operands.

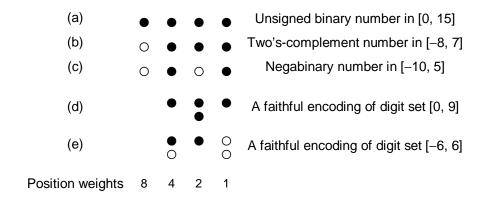

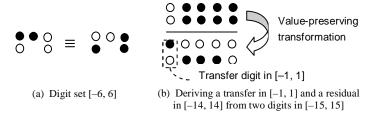

In describing arithmetic algorithms and associated transformations, it is customary to denote an ordinary bit, or posibit, by a heavy dot (~), thus producing a visual representation of numbers and algorithm steps in "dot notation" (Fig. 1a). Using a small hollow circle (™) to denote a negabit allows us to visualize 2's-complement numbers (Fig. 1b), negabinary or radix-(−2) numbers (Fig. 1c), and other representations formed by a specific mix of posibits and negabits in an extended dot notation. Redundant representations, with multiple dots in some positions, allow us to take advantage of their carry-free arithmetic property. Additionally, representational redundancy can lead to faithful representation of arbitrary digit sets such as [0, 9] (Fig. 1d) and [−6, 6] (Fig. 1e), which would otherwise have to be encoded using the wider ranges of [0, 15] and [−8, 7] (e.g., as in Figs. 1a and 1b), respectively.

It is the mixed use of arbitrary combinations of posibits and negabits in various bit positions (e.g., Fig. 1e) that forms the focus of this paper. In general, there may be several WBS encodings for a given digit set. For example, a collection of 6 negabits and 6 posibits, all weighted 1, also faithfully represent [-6, 6]. However, 2-deep or canonical WBS encodings (i.e., those containing

at most two bits in each binary position, as in Fig. 1) are preferred due to the possibility of more efficient implementation of arithmetic operations [Jabe05].

Fig. 1. Number representations of varying ranges in extended dot notation.

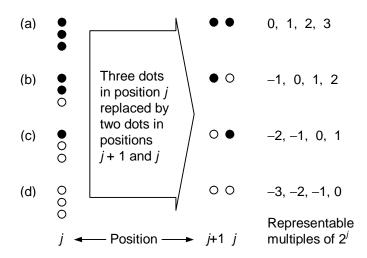

Fig. 2. Range-preserving transformations for WBS encodings.

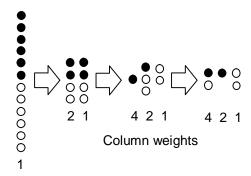

Fig. 3. Four faithful WBS representations of the digit set [-6, 6].

Any noncanonical WBS encoding can be converted to an equivalent canonical one using the range-preserving transformations of Fig. 2 to redistribute the extra dots in columns with more than 2 dots. Some results on WBS encodings, and associated arithmetic algorithms, follow immediately from the preceding discussion. For example, it is easy to see that any arbitrary digit set  $[-\alpha,\beta]$  can be faithfully represented using canonical (2-deep) WBS encoding; simply encode the set with  $\alpha$  negabits and  $\beta$  posibits of weight 1 and then apply the transformations of Fig. 2 in multiple rounds to reduce the depth to 2. Figure 3 depicts such transformations for  $\alpha = \beta = 6$ . Also, adding two WBS-encoded numbers can be viewed as the operation of depth reduction from 4 to 2, where the depth of 4 results from aligning the corresponding positions of the 2-deep operands. Finally, subtraction can be converted to addition by changing posibits to negabits, and vice versa, in the subtrahend.

In this paper, we aim to promote the use of WBS and inverted encoding of negabits (IEN) in the design of digital arithmetic circuits. Therefore, we reproduce relevant examples (Examples 1 and 3 in Section 2, and Examples 4-6 in Section 4) from some of the previously published works [Jabe08], [Jabe10a], and our corresponding conference paper [Jabe10b]. Furthermore, we present an efficient method for converting any canonical WBS encoding to any desired 2-deep encoding (see Example 7 in Section 4). In particular, conversion from 2-deep WBS to BSD is important due to ease of converting the latter to its equivalent 2's-complement number. As another new example, we present the design strategy for a modulo- $(2^n + 1)$  multiplier (see Example 8 in Section 4), where we show how WBS and IEN techniques help in reducing the design effort and increase the design reliability.

# 2. Representations and Algorithms

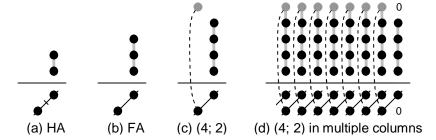

One of the important notions in the design of digital circuits for arithmetic-intensive and other applications is that of bit compression. For example, a half-adder (HA) can be viewed as a dot redistribution tool that takes two dots in the same column and produces one dot each in the same and the next higher position, as depicted in Fig. 4a. Similarly, a full-adder (FA), also

known as (3; 2)-counter, compresses three dots to two dots, corresponding to the sum and carry bits, as shown in Fig. 4b. When applied to multiple columns of 3 dots at once, this leads to reduction of 3 binary numbers to two binary numbers in a scheme known as carry-save addition. Finally, the (4; 2)-compressor of Fig. 4c is capable of compressing a column of 4 dots into 2 dots in adjacent columns, plus a carry bit that is sent to the next higher column. This is possible because 4 dots in a column when combined with an incoming carry (the fifth dot) represent a value in [0,5] and thus can be represented by one dot of the same weight and 2 dots of double that weight (Fig. 4d).

In the rest of this section, we present three examples to illustrate the applications and advantages of our unifying framework.

Fig. 4. Basic bit compression and redistribution operations in dot notation.

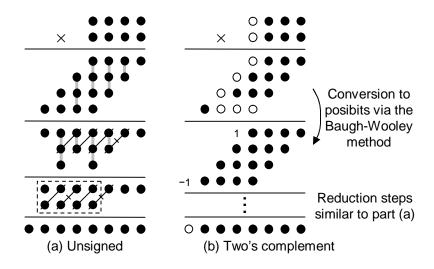

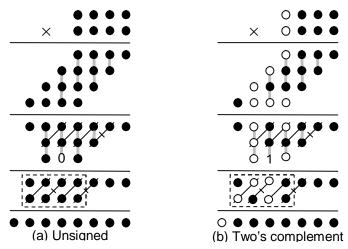

**Example 1** [Unsigned and 2's-complement multiplication]: Steps of conventional unsigned multiplication and 2's-complement multiplication based on Baugh-Wooley [Baug73] scheme for 4-bit operands are depicted in Figs. 5a and 5b, respectively. The essence of the Baugh-Wooley conversion step is the replacement of any negabit -b by the posibit 1-b (logical complement of b) and the constant negabit -1. Constant negabits are then gradually shifted to the left, and eventually discarded at the left end [Parh10], using the identity  $(0-1)_{two} = (-1-1)_{two}$ . However, Fig. 5b is a demonstration of our new interpretation of the Baugh-Wooley technique, with the use of negabit symbols. The three horizontally aligned negabits, in the bottom row of partial products, collectively represent a negative number (e.g., -xyz) that can be replaced by a 2's-complement number (e.g.,  $-1 \overline{x} \overline{y} \overline{z} + 1$ ) composed of a "-1" in the column of the leftmost

posibit, inversion of the 3 negabits regarded as posibits, and a "1" in the intermediate column. The same is true for the other 3 diagonally aligned negabits. Therefore, we get at the all-posibit partial products, with the two 1s (-1s) becoming a single 1 (-1) in the next more significant column. The partial products with negabits are just for illustration purpose and the all-posibit partial products are directly generated via an AND/NAND matrix, where the NAND gates produce the posibits that correspond to the aforementioned negabits. c

Fig. 5. Integer multiplication viewed as bit compression and addition.

**Example 2** [Partial-product generation in mod- $(2^n + 1)$  multiplication]: In mod- $(2^n + 1)$  multiplication, each posibit c in position n + i ( $0 \le i \le n - 1$ ) of a partial product is ruled by Eqn. 1, where  $c^-$  denotes a negabit whose arithmetic value equals -c and  $\overline{c} = 1 - c$ . Thus, a posibit c of weight  $2^{n+i}$  may be removed and a negabit  $c^-$  of weight  $2^i$  introduced instead.

$$\left| 2^{n+i} c \right|_{2^{n}+1} = \left| 2^{i} (2^{n} + 1 - 1) c \right|_{2^{n}+1} = 2^{i} (-c) = 2^{i} c^{-} = 2^{i} \overline{c} - 2^{i}$$

(1)

Based on this transformation, Fig. 6 illustrates a dot-notation representation of mod- $(2^n + 1)$  partial product generation for n = 4. The product  $\bullet_4 \times \bullet_4$ , of the most-significant bits (MSBs), originally weights  $2^{2n}$  and since  $2^{2n} = (2^n + 1)(2^n - 1) + 1$ , it appears as a posibit in position 0. Note that each operand is represented with n + 1 bits, with MSB being 1 only for  $2^n$ .

The previously proposed partial product reduction schemes (e.g., [Verg07]) require that each negabit  $c^-$  be replaced with a posibit  $\overline{c}$  and a constant negabit -1, a scheme that entails a nontrivial algorithm to compute the collective value of the constant negabits to form a new operand below the partial products. We will see in Section 3 that inverted encoding of negabits allows us to manipulate the negabits directly, thus widening the design space, saving some design effort, possibly circuit resources, and latency. c

|   | $ullet_4$ | $\bullet_3$ | $ullet_2$    | $ullet_1$    | $ullet_0$    |

|---|-----------|-------------|--------------|--------------|--------------|

| × | $ullet_4$ | •3          | $ullet_2$    | $ullet_1$    | $ullet_0$    |

|   |           | <b>●</b> 03 | $ullet_{02}$ | <b>●</b> 01  | $ullet_{00}$ |

|   |           | <b>●</b> 12 | $ullet_{11}$ | <b>●</b> 10  | $\circ_{04}$ |

|   |           | <b>●</b> 21 | <b>●</b> 20  | $\circ_{14}$ | $\circ_{13}$ |

|   |           | <b>●</b> 30 | 024          | $\circ_{23}$ | $\circ_{22}$ |

|   |           | 034         | 033          | $\circ_{32}$ | $\circ_{31}$ |

|   |           | 043         | $\circ_{42}$ | $\circ_{41}$ | $\circ_{40}$ |

|   |           |             |              |              | $ullet_{44}$ |

Fig. 6. Partial product generation in modulo-17 multiplication.

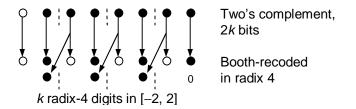

**Example 3** [Booth recoding for radix-4 multiplication]: Booth recoding can be more readily understood with the help of WBS. For example, the modified (i.e., radix-4) booth recoding, is essentially converting a 2's-complement number to its equivalent number in the minimally redundant radix-4 number system (i.e., conversion from the digit set [0, 3] to [-2, 2]). Let  $Y = y_{2n-1}^- y_{2n-2} \dots y_{2i+1} y_{2i} y_{2i-1} \dots y_1 y_0$ , where a "-" superscript identifies a negabit, represent a 2's complement number to be Booth recoded. This can be accomplished by simply shifting each posibit  $y_{2i+1}$  one binary position to left and filling its place by a negabit  $y_{2i+1}^-$  with the same logical state (see Fig. 7). This process leads to a canonical WBS representation of the desired minimally redundant radix-4 number, where the  $i^{th}$  radix-4 digit is represented by a doubled negabit  $y_{2i+1}^-$  and two posibits  $y_{2i}$  and  $y_{2i-1}$ . Note that this transformation is just an easier interpretation of the conventional modified booth recoding, which is of pedagogical value. Otherwise, Eqn. 2 for generating the Booth selection signals  $S_i$  (sign),  $T_i$  (twice or shifted), and  $O_i$  (One) remain the same. c

$$S_i = y_{2i+1}^-, \quad T_i = \overline{y_{2i+1}}^- y_{2i} y_{2i-1} \vee y_{2i+1}^- \overline{y_{2i} y_{2i-1}}, \quad O_i = y_{2i} \oplus y_{2i-1}$$

(2)

Fig. 7. Justification of modified Booth's recoding via extended dot notation.

## 3. Inverted Encoding of Negabits

The conventional representation of negative numbers or negative component of redundant numbers is based on assigning negative weights to whole numbers or digits. For example, sign-magnitude representation uses a separate sign bit that can be interpreted as the sign of the whole number. In the n-bit 2's-complement representation of binary numbers, the most significant bit is considered to have the negative weight  $-2^{n-1}$ . The  $\langle n, p \rangle$  encoding of a binary signed digit in radix-2 position i uses a pair of  $\pm 2^i$ -weighted bits [Parh90]. Finally, the digit set [-9,9] is represented as two 4-bit numbers with oppositely signed weights [Nikm06].

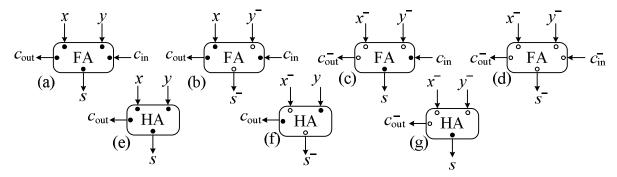

We have previously introduced the concept of negative bit (negabit for short) instead of negatively weighted bit [Jabe02], which simplifies some number representations, as was used in Figs. 1-3 (Section 1) and Examples 1-3 (Section 2). However, recalling Example 2, in reducing the partial products of Fig. 6, one cannot directly use the standard reduction cells such as HAs, FAs, and other compressors and counters. A simple solution for this kind of problems was offered in [Jabe05] via the introduction of inverted encoding of negabits (IEN), that is, assigning the logical state 0 (1) to arithmetic value –1 (0). This is the opposite of conventional encoding in 2's-complement numbers, where the most significant bit equals 0 (1) for positive (negative) values. This reverse convention turns out to be quite rewarding. It has been shown elsewhere [Jabe05] that with IEN any equally weighted triple mix of posibits and negabits can be summed up correctly with a standard full adder. Half adders and other counters and compressors can similarly accept any mix of posibits and negabits, generating correct results as if they were functioning on posibits only (see Figs. 8 and 9, with further relevant explanations to follow).

Fig. 8. Full-adders and half-adder as universal combiners of posibits and negabits.

This use of standard cells is very important, for it offers the advantage of being able to choose from a variety of readily available designs that are optimized based on different criteria (e.g., latency, area, and power) for a multitude of implementation technologies [Chen05]. To process conventional negabits in the same way, inverters are typically inserted on some inputs/outputs of standard cells [Korn05], adding some latency, compromising circuit regularity, and introducing the need for area/power re-optimization. Note that even though the latency of an inverter is fairly small, removing one or more inversion layers in a carry-free adder that typically needs only 4-8 logic levels leads to nontrivial speed improvements.

The key to improvements resulting from IEN is the property that their logical and arithmetic values vary in the same direction. Representing the value -1 as logical 0 and the value 0 as logical 1 is in effect a biased representation with a bias of 1. A posibit is unbiased (has a bias of 0), given that its logical and arithmetic values are identical. Note that as long as the sum of biases for the inputs matches those of the outputs, no adjustment will be needed when posibits and negabits are combined as if they were all posibits. For example, Fig. 8 shows schematic representations of a full (half) adder used to combine a set of 3 (2) bits, which includes from 0 to 3 (2) negabits [Jabe05]. Note that when a negabit is sent to the next higher position, its bias is effectively doubled. Thus, the sums of input and output biases are balanced in all seven cases depicted in Fig. 8. Recall that a standard full (half) adder operates on posibits in a way that enforces the identity  $x + y + c_{in} = 2c_{out} + s$  ( $x + y = 2c_{out} + s$ ), with numerical details shown in Eqn. 3. For clarity in studying Fig. 8, the reader is reminded that a "–" superscript identifies a negabit.

(a)

$$0+0+0=0+0$$

(b)  $0+0+1=0+1$  (c)  $0+1+1=2+0$  (d)  $1+1+1=2+1$  (e)  $0+0=0+0$  (f)  $0+1=0+1$  (g)  $1+1=2+0$  (3)

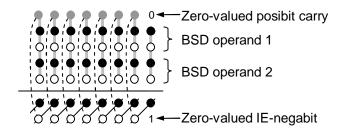

Figure 9 depicts an instance of the standard (4; 2)-compressor of Fig. 4c acting as a redundant binary adder (RBA), or adder with binary signed-digit (BSD) inputs. The best RBA cell that we have encountered is based on a custom design [Kim01] and has a latency of 3 XOR gates, the same as a conventional (4; 2) compressor, with gate counts also being comparable. It is worth noting that the design just mentioned uses a 2-bit encoding that is the same as the  $\langle n, p \rangle$  encoding with inversely encoded negabits (IE-negabits). However, because of the ad hoc approach, the design effort is much greater and the resulting circuits cannot benefit from regular performance improvements on standard cells. The universal (4; 2)-compressors of Fig. 9, on the other hand, can be replaced by any available (4; 2)-compressor circuit.

Fig. 9. Using (4; 2)-compressors as redundant binary adders.

There are also other highly optimized compressors, exemplified by (5; 2) compressors [Chan04], that may prove beneficial in reducing arrays of mixed posibits and negabits, where the depth is not a multiple of 4 (see Example 8). This is yet another confirmation that the use of highly optimized standard cells is preferable to ad hoc designs, whenever possible.

## 4. Implementations and Applications

Use of IEN and WBS encoding has been shown to enhance creativity in designing arithmetic circuits that often leads to better performance as well. For example, hybrid-redundant adders [Phat01] have been redesigned in a universal manner in [Jabe06], from which the design of a minimally redundant adder is reproduced in Example 4. A highly efficient maximally

redundant signed digit adder [Jabe10a], and a less redundant version based on IEN [Gorg11], have been recently proposed, where the use of IEN leads to power and area savings via the elimination of the need for sign extension. Another interesting property of WBS encoding and IEN is the value-preserving transformation on a collection of bits that represent a symmetric range of negative and positive values. As it turns out, in such cases, interchanging the posibits with negabits and vice versa without changing the logical states preserves the actual value of the bit collection [Jabe10a]. This property is further explained in Example 5 and used in Example 6 to lead to a yet another new interpretation of Baugh-Wooly 2's complement multiplication scheme.

Use of off-the-shelf HAs, FAs, counters, and compressors, exemplified by (4; 2)-compressors, to reduce the depth of a WBS encoding (e.g., partial product reduction) often leads to a canonical 2-deep WBS representation with an arbitrary mix of posibits and negabits. This mix can be added via any conventional carry-propagate adder (CPA). However, the 1-deep result can hold posibits and negabits in arbitrarily weighted positions. This undesired phenomenon can be avoided via a small preprocessing step prior to CPA, as described in Example 7 for the first time in this paper. Finally, we take up Example 2 and show how the partial products of modulo- $(2^n + 1)$  multiplier can be summed up with standard reduction cells via IEN (See Example 8).

**Example 4** [Simplified minimally redundant radix- $2^h$  SD addition]: A straightforward implementation of the digit-level addition algorithm for radix- $2^h$  signed digit (SD) number systems [Parh90] implies three O(log h)-latency carry-propagating operations in sequence. A radix- $2^h$  signed digit set is often denoted by the integer interval  $[-\alpha, \alpha]$ , with the redundancy index  $\rho = 2\alpha + 1 - 2^h$ . For  $\rho \ge 2$ , the sum digit in position i depends on the operand digits in the same position and those of position i - 1, vis a vis carry-free addition [Parh90]. For  $\rho = 1$  (e.g., with  $\alpha = 2^{h-1}$ ), however, it depends also on the operands digits in position i - 2. Here we provide a particular bit-level implementation, for  $\rho = 1$ , where there is only one h-bit carry-propagating operation and each bit within the sum digit in position i depends only on the bits of two operand digits; either on the bits of digits in positions i and i - 1 or those of positions i - 1 and i - 2.

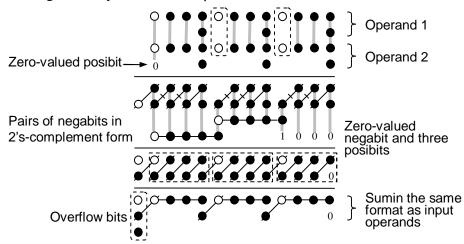

Fig. 10 depicts a conceptual representation of stored-posibit addition as a case of symmetric extended hybrid-redundant number system, where "extended" refers to our allowing negabits as well as posibits in nonredundant positions [Jabe08]. Recall that ordinary hybrid redundancy uses only posibits in such positions [Phat01]. The particular number system shown is periodic, with a period of 4 positions, and thus corresponds to a radix-16 (i.e., h = 4) generalized signed-digit representation with the minimally redundant digit set [-8, 8]. The first stage of the addition process, depicted in Fig. 10, converts pairs of negabits in the input operands, with the exception of those in the leftmost position, to 5-bit 2's-complement numbers (see the dashed boxes). The rest of the process consists of standard bit compression and a final set of 4-bit additions. Note that the stored posibit of the sum digit in position i does not depend on the operand digits in the same position and the bits of the 2's-complement main part do not depend on the operand digits in position i-2. This conforms to the general result in [Parh90] under limited-carry addition with  $\rho = 1$ . That is, as a whole, each sum-digit is a function of digits in three consecutive positions of the operands. However, the main part (the stored posibit) of position i depends on only the digits in positions i and i-1 (i-1 and i-2). Therefore, the digit dependency is the same as that existing for carry-free cases of  $\rho \ge 2$ . C

Fig. 10. Dot-notation representation of symmetric hybrid-redundant addition.

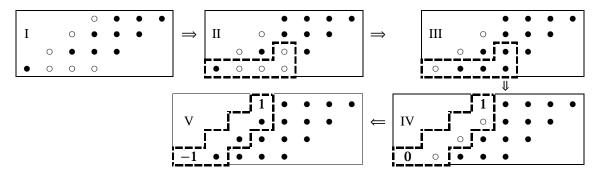

**Example 5** [Value-preserving polarity inversion in faithfully represented balanced signed digits]: Consider an  $\langle n, p \rangle$  encoded binary signed digit and also the rightmost representation of the digit set [-6, 6] in Fig. 3. Such faithfully represented signed digit sets are invertible by exchanging posibits and negabits, as shown in Fig. 11a. We know that identical bit assignments to both representations of Fig. 11a yields equal arithmetic values [Jabe10a]. This provides the opportunity of regarding posibits (negabits) as if they were negabits (posibits), where such an interpretation would facilitate the design process. For example, Fig. 11b represents the essence of the transfer extraction scheme of a radix-16 maximally redundant signed-digit (MRSD) adder, whit each redundant signed digit in [-15, 15] and encoded as a 5-bit two's-complement number. The carry-free addition process requires the extraction of a weight-16 transfer digit  $t_{i+1} \in [-1, 1]$ from operand digits in position i, whose sum ranges from -30 to 30, leaving a residual in [-14,14]. Inverting the polarity of all bits in the top operand and the least-significant bit in the lower operand preserves the arithmetic value of the transformed bits, given that the transformation in position j increases (decreases) the arithmetic value by  $2^{j}$ . This cost-free transformation (inversion occurs in the way the bits are viewed, rather than via an inversion gate) provides a weight-16 negabit/posibit pair in the most-significant position that can serve as the desired  $t_{i+1}$ , except in a few input cases that are detectable via simple exception handling logic [Jabe10a].

Fig. 11. Cost-free value-preserving transformations.

A similar value-preserving polarity inversion can be used for yet another simple justification of the Baugh-Wooly method. This is illustrated in Fig. 12, in which the partial products of Part I are generated with NAND gates, where exactly one of the two bits is a negabit. Part II is exactly the same as Part I, except for a negabit/posibit position swap for better illustration of the dashed-

border bit collection whose polarities are inverted in Part III. The posibit constant 0 and the IE-negabit constant 1 (with arithmetic worth of 0) are inserted (see Part IV) to allow for the second transformation, again illustrated by dashed-border bit collections. Note that after polarity inversion, the constant 0 (1) is represented by a negabit -1 (posibit 1) in V, where the bit collection is exactly the same as the bottom part of Fig. 5b. The reader is reminded that, as in Fig. 5b, the bits of Part V are directly generated via a NAND/AND matrix from the bits of the 2's-complement operands. c

Fig. 12. Alternative justification of the Baugh-Wooley multiplication method.

**Example 6** [Identical partial product reduction tree for unsigned and 2's-complement multiplication]: Fig. 13 represents an implementation of 4-bit 2's-complement multiplication using energy efficient NAND gates [Abid08], wherever the inputs of a partial product generation cell are of opposite polarities, leading to a tree reduction part assuming the use of IE-negabits for the partial products. The final adder uses a half adder in position 3 and full adders in the next three positions (see cell (c) in Fig. 8 for explanation on how the full adders work). Therefore, the required circuitry is exactly the same as the one needed for Fig. 5b. However, the main advantage here is again pedagogical, given the simple concept behind the scheme of Fig. 13b in comparison to that of Baugh-Wooley (Fig. 5b). c

Fig. 13. Unsigned or signed multiplication with identical tree reduction circuits.

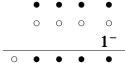

**Example 7** [Conversion from 2-deep WBS to 2's complement]: The operation of the final adder in Fig. 13b is a special case of the general problem of converting a 2-deep WBS number to its 2's complement equivalent. It is easy to see that the simple adder solution used for Fig. 13b works for converting an  $\langle n, p \rangle$ -encoded BSD number, with IE-negabits, to 2's complement, provided a forced carry-in is used in the form of an IE-negabit  $1^-$  with arithmetic value 0. For example, the situation for a conversion from 4-bit BSD to 5-bit 2's-complement representation is depicted in Fig. 14, where each of the four full adders receiving 2 negabits and 1 posibit produces a posibit sum and a negabit carry, as in cell (c) in Fig. 8. However, this simple method for the special case of BSD numbers does not always work for the aforementioned general case.

Fig. 14. BSD-to-2CL conversion via binary addition with  $c_{\rm in} = 1$ .

One solution is to first convert the source 2-deep WBS number to its BSD equivalent, and then follow this by simple addition. The conversion to BSD, as summarized in Table I, is possible by means of an Inverter (I), a half-adder (HA), or an excess-1 half-adder (HA<sup>+1</sup>) in each binary position  $i \ge 0$ . The cell choice depends on the bit combination in position i and the incoming bit from the possible HA or HA<sup>+1</sup> in position i - 1, during the conversion process. Recall that a variable or parenthesized expression with a "–" superscript denotes a negabit. The bit that comes into position 0 can be assumed to be either a posibit or a negabit.

Table I. Conversion from 2-deep WBS to BSD  $(\bigoplus$  is XOR;  $\bigcirc$  represents XNOR).

| Case     | Source<br>Incoming |                       | Target (in 2 columns) |                                                |     |                              | Cell      |

|----------|--------------------|-----------------------|-----------------------|------------------------------------------------|-----|------------------------------|-----------|

|          | Dot                | Symbol                | Dot                   | Symbol                                         | Dot | Symbol                       | type      |

| 1        | •                  | х                     |                       | X                                              | 0   | $(\overline{x})^-$           | I         |

| 1        | •                  | у                     |                       | χ<br>                                          | •   | У                            |           |

| 2        | •                  | х                     |                       |                                                | •   | X                            |           |

|          | 0                  | <i>y</i> -            |                       |                                                | 0   | <i>y</i> -                   |           |

| 3        | 0                  | <i>x</i> <sup>-</sup> |                       |                                                | 0   | <i>x</i> <sup>-</sup>        |           |

|          | •                  | у                     |                       |                                                | •   | $\frac{y}{\overline{x}}$     |           |

| 4        | 0                  | x <sup>-</sup>        | 0                     | <i>x</i> -                                     | •   |                              | I         |

|          | 0                  | <i>y</i> -            |                       |                                                | 0   | <i>y</i> <sup>-</sup>        |           |

| 5        | •                  | <i>x</i><br><i>x'</i> | • xvx'                | r\/r'                                          | 0   | $(x \odot x')^-$             | $HA^{+1}$ |

|          | •                  | <i>у</i>              |                       | •                                              | у   |                              |           |

|          | •                  | x                     | •                     | xx'                                            | •   | $x \oplus x'$                | НА        |

| 6        |                    | x'                    |                       |                                                |     |                              |           |

|          | 0                  | $\frac{y^-}{x^-}$     |                       |                                                | 0   | <i>y</i> -                   |           |

| 7        | 0                  | x'                    | 0                     | $\circ \left  (x^- \vee x'^-)^- \right $       | 0   | $(x^- \odot x'^-)^-$         | $HA^{+1}$ |

|          | •                  | у                     |                       | ,                                              | •   | y                            |           |

|          | 0                  | <i>x</i> <sup>-</sup> | 0                     | (x <sup>-</sup> x' <sup>-</sup> ) <sup>-</sup> |     | ~- ( ) «/-                   | НА        |

| 8        | 0                  | x'-                   |                       |                                                | •   | $x^- \oplus x'^-$            |           |

|          | 0                  | <i>y</i> -            |                       |                                                | 0   | <i>y</i> -                   |           |

| 9        | •                  | X<br>/-               | •                     | _ x                                            | 0   | $(x \oplus x'^{-})^{-}$      |           |

|          |                    | x'-                   |                       | •   x'-                                        |     | (" \( \psi \) " \( \gamma \) | HA        |

|          | •                  | У                     |                       |                                                | •   | У                            |           |

| 10       | 0                  | x<br>x'-              | 0                     | $(x \vee x'^-)^-$                              | •   | $x \odot x'^-$               | $HA^{+1}$ |

|          | 0                  | ν-                    |                       | ,                                              | 0   | ν-                           |           |

| Position |                    | i                     |                       | i+1                                            |     | i                            |           |

Deciding on the actual cell for each binary position at design time is a sequential process that is further explained in Example 8. However, as is evident from the left target column in Table I (i.e., position i+1), the incoming bit to position i+1 does not depend on the one for position i. Therefore, the actual run time delay is at most equal to that of a single XOR gate. c

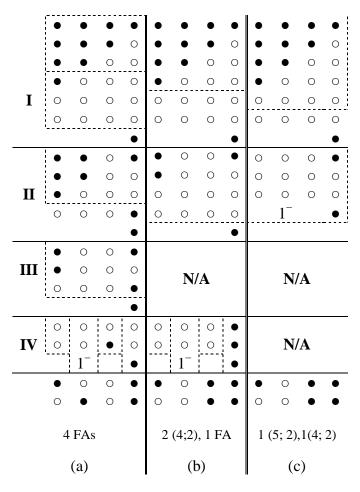

**Example 8** [Modulo- $(2^n + 1)$  multiplication]: The partial product generation (PPG) scheme of Fig. 6 allows energy-efficient NAND gates to replace the original AND gates for generating end-around partial product IE-negabits. Figure 15a depicts a carry-save adder (CSA) scheme for partial product reduction (PPR), where each dashed box in Stages I to III represents an n-bit CSA (n = 4) and stage IV simply converts the result to a representation that can lead to the desired product via any n-bit adder. This stage uses FA, HA, HA<sup>+1</sup>, HA, from right to left, respectively. Performance is enhanced in Figs. 15b and 15c by also allowing the use of (4; 2) and (5; 2) compressors. Note that the cells used in each of the three designs belong to the set of standard arithmetic building blocks, often available in multiple optimized forms for mapping onto FPGAs, custom VLSI implementation, and other digital design styles [Aguil 1]. c

Fig. 15. Three modulo-17 PPR.

The number of partial products for the scheme just explained in Example 8 is n + 3. This can be reduced to n at the expense of more complex 3-gate-delay PPG and custom wiring of the inputs to CSA tree, so as to keep the extra PPG delay off the critical path [Verg07]. Unfortunately, to apply a similar scheme in that work for reduction trees with more efficient (4; 2) and (5; 2) compressors, as in Figs. 15b and 15c, would require redesigning the compressors' internal wiring, thus jeopardizing all the test, optimization, and synthesis efforts implicit in their designs. Furthermore, custom wiring, as used in the case of n = 4 [Verg07], may not always be beneficial. For example, the left side of Table II shows the number of CSA (FA) levels, and the corresponding delay in terms of XOR gates, for  $p \in [4,13]$  partial products (i.e.,  $n \in [4,10]$ ). Only for n = 4, two levels are saved compared with n + 3 = 7 partial products. In cases where  $n \in [5,9]$ , only one level is saved compared with  $n + 3 \in [8,12]$ . There are 5 CSA levels for both n = 10 and n + 3 = 13 partial products, implying no saving. The right side of Table II shows the number of reduction stages and the reduction cell types used. For example, for n + 3 = 7, the critical delay path consists of two (4; 2) compressors based on Fig. 15b. Note that the figures presented in Table II consider neither Stage IV of Fig. 15 nor the half adder stage (due to constant partial product) of [Verg07].

Table II. Partial product reduction with different reduction cells

|      |         |    | Reduction cells |       |                    |       |  |

|------|---------|----|-----------------|-------|--------------------|-------|--|

|      |         | p  | FA              | # XOR | (5; 2), (4; 2), FA | # XOR |  |

|      |         | 4  | 2               | 4     | 0, 1, 0            | 3     |  |

|      |         | 5  | 3               | 6     | 1, 0, 0            | 4     |  |

|      |         | 6  | 3               | 6     | 0, 2, 0            | 6     |  |

| n    | $\prec$ | 7  | 4               | 8     | 0, 2, 0            | 6     |  |

|      |         | 8  | 4               | 8     | 0, 2, 0            | 6     |  |

|      |         | 9  | 4               | 8     | 1, 1, 0            | 7     |  |

| n +3 | -≼      | 10 | 5               | 10    | 1, 1, 0            | 7     |  |

|      |         | 11 | 5               | 10    | 2, 0, 0            | 8     |  |

|      |         | 12 | 5               | 10    | 0, 3, 0            | 9     |  |

|      |         | 13 | 5               | 10    | 0, 3, 0            | 9     |  |

The arguments regarding the dubious advantage of custom wiring notwithstanding, the method of [Verg07] can be applied here to achieve an n-deep WBS partial product matrix for modulo  $2^n + 1$  multiplication as in Fig. 16, with due explanations to follow.

| $ullet_4$ | $\bullet_3$     | $ullet_2$                                                              | ullet 1                                                                                                                                                                                                                               | $ullet_0$                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •4        | •3              | •2                                                                     | ullet1                                                                                                                                                                                                                                | $ullet_0$                                                                                                                                                                                                                                                                                                                   |

|           | <b>●</b> 03     | $ullet_{02}$                                                           | $ullet_{01}$                                                                                                                                                                                                                          | • <sub>00</sub>                                                                                                                                                                                                                                                                                                             |

|           | <b>●</b> 12     | $ullet_{11}$                                                           | • <sub>10</sub>                                                                                                                                                                                                                       | $\circ_{04}$                                                                                                                                                                                                                                                                                                                |

|           | <b>●</b> 21     | <b>●</b> 20                                                            | $\circ_{14}$                                                                                                                                                                                                                          | $\circ_{13}$                                                                                                                                                                                                                                                                                                                |

| I         | • <sub>30</sub> | $\circ_{24}$                                                           | $\circ_{23}$                                                                                                                                                                                                                          | $\circ_{22}$                                                                                                                                                                                                                                                                                                                |

|           | 034             | $\circ_{33}$                                                           | 032                                                                                                                                                                                                                                   | $\circ_{31}$                                                                                                                                                                                                                                                                                                                |

|           | 043             | $\circ_{42}$                                                           | $\circ_{41}$                                                                                                                                                                                                                          | $\circ_{40}$                                                                                                                                                                                                                                                                                                                |

|           |                 |                                                                        |                                                                                                                                                                                                                                       | <b>●</b> 44                                                                                                                                                                                                                                                                                                                 |

|           | <b>●</b> 03     | $ullet_{02}$                                                           | $ullet_{01}$                                                                                                                                                                                                                          | $ullet_0$                                                                                                                                                                                                                                                                                                                   |

|           | <b>●</b> 12     | <b>●</b> 11                                                            | <b>●</b> 10                                                                                                                                                                                                                           | $\circ_{13}$                                                                                                                                                                                                                                                                                                                |

| II        | <b>●</b> 21     | <b>●</b> 20                                                            | $\circ_{23}$                                                                                                                                                                                                                          | $\circ_{22}$                                                                                                                                                                                                                                                                                                                |

|           | <b>●</b> 30     | $\circ_2$                                                              | $\circ_1$                                                                                                                                                                                                                             | $\circ_0$                                                                                                                                                                                                                                                                                                                   |

|           | 03              |                                                                        |                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                             |

|           | <b>●</b> 03     | <b>●</b> 02                                                            | $ullet_{01}$                                                                                                                                                                                                                          | • <sub>0</sub> '                                                                                                                                                                                                                                                                                                            |

| III       | <b>●</b> 12     | <b>●</b> 11                                                            | <b>●</b> 10                                                                                                                                                                                                                           | $\circ_{13}$                                                                                                                                                                                                                                                                                                                |

|           | <b>●</b> 21     | <b>●</b> 20                                                            | $\circ_{23}$                                                                                                                                                                                                                          | $\circ_{22}$                                                                                                                                                                                                                                                                                                                |

|           | $\bullet_3$     | 0.                                                                     | $\circ_1$                                                                                                                                                                                                                             | $\circ_0$                                                                                                                                                                                                                                                                                                                   |

|           | I<br>II         | •4 •3 •03 •12 •21 I •30 •34 •43  •03 •12 II •21 •30 •3 •03 III •12 •21 | ●4 ●3 ●2  ●03 ●02  ●12 ●11  ●21 ●20  I ●30 ○24  ○34 ○33  ○43 ○42   ■03 ●02  ●12 ●11  II ●21 ●20  ●30 ○2  ○3  ■03 ●02  ■11  ■11  ■11  ■11  ■11  ■11  ■21 ■20 ■30 ■2 ■31 ■30 ■2 ■31 ■30 ■32 ■31 ■32 ■33 ■33 ■32 ■33 ■33 ■33 ■33 ■33 ■33 | ●4 ●3 ●2 ●1  ●03 ●02 ●01  ●12 ●11 ●10  ●21 ●20 ○14  I ●30 ○24 ○23 ○34 ○33 ○32 ○43 ○42 ○41  ■03 ●02 ●01  ■12 ●11 ●10  ■14 ●10  ■15 ●11 ●10  ■16 ●12 ●11 ●10  ■17 ●10 ■18 ●03 ●02 ●01 ■19 ●11 ●10 ■19 ●11 ●10 ■11 ●10 ■11 ●10 ■12 ●11 ●10 ■13 ●02 ●01 ■14 ●10 ■15 ●11 ●10 ■16 ●12 ●11 ●10 ■17 ●10 ■18 ●11 ●10 ■19 ●21 ●20 ○23 |

Fig. 16. Efficient modulo-17 PPG

The two negabit entries in the same column of Fig. 6, with one of the indices being 4 (e.g.,  $\circ_{14}$  and  $\circ_{41}$ ) and any other negabit in the same column (e.g.,  $\circ_{32}$ ), can be replaced by a new negabit which represents the true sum of the original negabits (e.g.,  $\circ_1$  in Fig. 16). This compression of three negabits into one is possible because when the most-significant bit of a modulo- $(2^n + 1)$  operand is 1, its other n bits are 0s. Thus,  $\bullet_{i4} + \bullet_{4i} + \bullet_{3(i+1)} = \bullet_{i4} \vee \bullet_{4i} \vee \bullet_{3(i+1)}$ , implying that  $\circ_i$  can be obtained by NORing  $\bullet_{i4}$ ,  $\bullet_{4i}$  and  $\bullet_{3(i+1)}$ , for  $0 \le i \le n-1$ . For the same reason, it holds that  $\bullet_{00} + \bullet_{44} = \bullet_{00} \vee \bullet_{44}$ , and thus the sum is represented by a single posibit  $\bullet_0$  in Fig. 16. To avoid the depth of 5 in the most significant column of Stage II in Fig. 16, we use the trick offered in [Verg07], replacing  $\circ_3$  with  $\bullet_3$  in the same column and another one in the rightmost column based on Eqn. 4. The reason is that the computation of  $\circ_3$ , as described by Eqn. 4, can be reformulated as in Eqn. 5. However, as before, we have  $\bullet_{34} + \bullet_{43} + \bullet_{30} = \bullet_{34} \vee \bullet_{43} \vee \bullet_{30}$ . The result is shown as the single posibit  $\bullet_3$  of Stage III in Fig. 16. Similarly, we have  $\bullet_0' = \bullet_0 + \bullet_{34} + \bullet_{43} = \bullet_{00} \vee \bullet_{44} \vee \bullet_{34} \vee \bullet_{34} \vee \bullet_{43}$ .

$$|2^{7}(\bullet_{34} + \bullet_{43})|_{17} = |8 \times (17 - 1)(\bullet_{34} + \bullet_{43})|_{17} = -8(\bullet_{34} + \bullet_{43}) = 8 \circ_{3}$$

(4)

$$|2^{7}(\bullet_{34} + \bullet_{43})|_{17} = |(17 \times 7 + 9)(\bullet_{34} + \bullet_{43})|_{17} = (8+1)(\bullet_{34} + \bullet_{43})$$

(5)

With the 4-deep partial product matrix of Stage IV in Fig. 16, we need only two CSA levels to get at a 2-deep matrix. However, a half-CSA stage is required to convert the latter to a form suitable for input to any binary adder, including the inverted end around carry adder of [Verg07]. A similar half-CSA stage is used in [Verg07] due to an extra constant partial product (see Example 2). Note that Stages I, II, and III are used merely for illustration; the actual PPG circuitry would directly generate the bit matrix of Stage IV.

Advantages of the modular multiplier design of Example 8 in comparison with previous designs (e.g., [Verg07]) include easier exploration of the design space, simpler conceptual design, and use of a variety of standard optimized cells.

## 5. Conclusion

By using several examples from our previous works and introducing two new case studies, we have demonstrated the advantages of intermixing posibits and negabits as elements of weighted bit sets for use in representing signed digit sets or for direct representation of integers in a desired range. More specifically, the advantages fall into the two categories of pedagogical (better understanding) and practical (more efficient hardware realizations). On the pedagogical front, viewing a number of different transformations, such as Booth recoding and column compression, in a unified way engenders a better understanding of why these methods work and how variants of such methods can be devised. Practical benefits include both a reduction in design effort and improvements in design parameters such as cost, speed, and/or power consumption. These practical benefits are direct consequences of our unified design strategy, based on the exclusive use of highly optimized standard building blocks or cells, for realizing arithmetic operations on representations composed of weighted posibits and negabits.

The design flow for implementing an arithmetic operation on redundant operands based on the digit set  $[-\alpha, \beta]$  may consist of the following steps:

- a) Start with  $\alpha$  negabits and  $\beta$  posibits, all equally weighted (i.e., in the same column) and use the transformation of Fig. 2 in multiple rounds, until a 2-deep WBS encoding of the digit set is obtained.

- b) Design the required arithmetic circuits as if all the bits were posibits, but consider the polarity of the bits in the intermediate results as the output bits of the relevant cells (e.g. those in Fig. 8).

- c) Use Table I to convert the final WBS encoding to the desired output format.

Even though we have used this method, and the associated inverted encoding of negabits, in our designs before, we thought that explicating the underpinnings of our design strategy, outlining its intuitive basis, and listing some of the key applications would be beneficial to designers of signal processing and other VLSI systems. We have augmented the aforementioned known design examples with two new applications specifically developed for this presentation: WBS-to-BSD-to-2CL format conversion, and modulo- $(2^n + 1)$  multiplication. The examples offered here are by no means exhaustive. Exploration of new application domains constitutes part of our plans for future work.

Our discussion in this paper has been qualitative, pointing to advantages in terms of easier exploration of design space, simpler conceptual design (thus, design time reduction and error avoidance), and use of highly optimized standard cells that are available in the literature and in various design libraries. The use of standard arithmetic building blocks allows our designs to benefit from the continuous innovations that lead to faster, more compact, and lower-power components such as half-adders, full-adders, and bit compressors. Quantitative assessments of the benefits would be possible only for specific applications, after full circuit-level implementation. We have not done this in the current paper, but instead refer the reader to our previous publications, cited in the references, which do offer quantitative evaluations and comparisons.

## References

- [Abid08] Abid, Z., H. El-Razouk, and D. A. El-Dib, "Low Power Multipliers Based on New Hybrid Full Adders," *Microelectronics J.*, Vol. 39, pp. 1509-1515, 2008.

- [Agui11] Aguirre-Hernandez, M. and M. Linares-Aranda, "CMOS Full-Adders for Energy-Efficient Arithmetic Applications," *IEEE Trans. VLSI Systems*, Vol. 19, No. 4, April 2011.

- [Aviz61] Avizienis, A., "Signed-Digit Number Representation for Fast Parallel Arithmetic," *IRE Trans. Electronic Computers*, Vol. 10, pp. 389-400, 1961.

- [Baug73] Baugh, C. R. and B. A. Wooley, "A Two's Complement Parallel Array Multiplication Algorithm," *IEEE Trans. Computers*, Vol. 22, No. 6, pp. 1045-1047, December 1973.

- [Chan05] Chang, C.-H., J. Gu, and M. Zhang, "A Review of 0.18-µm Full Adder Performances for Tree Structured Arithmetic Circuits," *IEEE Trans. VLSI Systems*, Vol. 13, No. 6, pp. 686-695, June 2005.

- [Gorg11] Gorgin S. and G. Jaberipur, "A Family of Signed Digit Adders," in Proc. of the 20<sup>th</sup> IEEE Symposium on Computer Arithmetic, pp. 112-120, July, 25-27, 2011, Tubingen, Germany.

- [Jabe02] Jaberipur, G., B. Parhami and M. Ghodsi, "Weighted Bit-Set Encodings for Redundant Digit Sets: Theory and Applications," *Proc. 36th Asilomar Conf. Signals Systems and Computers*, pp. 1629-1633, November 2002.

- [Jabe05] Jaberipur, G., B. Parhami, and M. Ghodsi, "Weighted Two-Valued Digit-Set Encodings: Unifying Efficient Hardware Representation Schemes for Redundant Number Systems," *IEEE Trans. Circuits and Systems I*, Vol. 52, No. 7, pp. 1348-1357, July 2005.

- [Jabe06] Jaberipur, G., B. Parhami, and M. Ghodsi, "An Efficient Universal Addition Scheme for All Hybrid-Redundant Representations with Weighted Bit-Set Encoding," *Journal of VLSI Signal Processing*, Vol. 42, No. 2, pp. 149-158, February 2006.

- [Jabe08] Jaberipur, G. and B. Parhami, "Constant-Time Addition with Hybrid-Redundant Numbers: Theory and Implementations," *Integration, the VLSI J.*, Vol. 41, No. 1, pp. 49-64, Jan 2008.

- [Jabe09] Jaberipur, G. and B. Parhami, "Unified Approach to the Design of Modulo-(2<sup>n</sup>± 1) Adders Based on Signed-LSB Representation of Residues, *Proc. 19th IEEE Int'l Symp. Computer Arithmetic*, 2009, pp. 57-64.

- [Jabe10a] Jaberipur, G. and S. Gorgin, "An Improved Maximally Redundant Signed Digit Adder," *Computers & Electrical Engineering*, Vol. 36, No. 3, pp. 491-502, May 2010.

- [Jabe10b] Jaberipur, G. and B. Parhami, "Posibits, Negabits, and Their Mixed Use in Efficient Realization of Arithmetic Algorithms," *Proc. 15th CSI Int'l Symp. Computer Architecture and Digital Systems*, pp. 3-9, 2010.

- [Kim01] Kim, Y., et al., "A Carry-Free 54b × 54b Multiplier Using Equivalent Bit Conversion Algorithm," *IEEE J. Solid-State Circuits*, Vol. 36, No. 10, pp. 312-317, October 2001.

- [Kore81] Koren,I. and Y. Maliniak, "On Classes of Positive, Negative, and Imaginary Radix Number Systems," *IEEE Trans. Computers*, Vol. 30, No. 5, pp. 312-317, May 1981.

- [Korn05] Kornerup, P., "Reviewing 4-to-2 Adders for Multi-Operand Addition," *J.VLSI Signal Processing*, Vol. 40, No. 1, pp. 143-152, May 2005.

- [Kuni93] Kuninobu, S., T. Nishiyama, and T. Taniguchi, "High Speed MOS Multiplier and Divider Using Redundant Binary Representation and Their Implementation in a Microprocessor," *IEICE Trans. Electronics*, Vol. E76-C, pp. 436-444, 1993.

- [Maki96] Makino, H., Y. Nakase, H. Suzuki, H. Morinaka, H. Shinohara, and K. Mashiko, "An 8.8-ns 54 × 54-Bit Multiplier with High Speed Redundant Binary Architecture," *IEEE J. Solid-State Circuits*, Vol. 31, No. 6, pp. 773-783, June 1996.

- [Meye07] Meyer-Baese, U., Digital Signal Processing with Field Programmable Gate Arrays, Springer, 3rd ed., 2007.

- [Nikm06] Nikmehr, H. and B. Philips, "Fast Decimal Floating-Point Division," *IEEE Trans. Computers*, Vol. 14, No. 9, pp. 951-961, September 2006.

- [Omon07] Omondi, A. and B. Premkumar, *Residue Number Systems: Theory and Implementation*, Imperial College Press, 2007.

- [Parh90] Parhami, B., "Generalized Signed-Digit Number Systems: A Unifying Framework for Redundant Number Representations," *IEEE Trans. Computers*, Vol. 39, No. 1, pp. 89-98, January 1990.

- [Parh10] Parhami, B., Computer Arithmetic: Algorithms and Hardware Designs, Oxford University Press, 2nd ed., 2010.

- [Phat01] Phatak, D. S. and I. Koren, "Constant-Time Addition and Simultaneous Format Conversion Based on Redundant Binary Representations," *IEEE Trans. Computers*, Vol. 50, No. 11, pp. 1267-1278, November 2001.

- [Radh00] Radhakrishnan, D. and A. P. Preethy, "Low-Power CMOS Pass Logic 4-2 Compressor for High-Speed Multiplication," Proc. 43rd IEEE Midwest Symp. Circuits and Systems, 2000, Vol. 3, pp. 1296-1298.

- [Sode86] Soderstrand, M. A., W.K. Jenkins, G.A. Jullien, and F.J. Taylor (eds.), *Residue Number System Arithmetic*, IEEE Press, 1986.

- [Taga85] Takagi, N., H. Yasuura, and S. Yajima, "High-Speed VLSI Multiplication Algorithm with a Redundant Binary Addition Tree," *IEEE Trans. Computers*, Vol. 34, No. 9, pp. 789–796, September 1985.

- [Tayl83] Taylor, F. J., Digital Filter Design Handbook, M. Dekker, 1983.

- [Verg07] Vergos, H. T. and C. Efstathiou, "Design of Efficient Modulo 2<sup>n</sup> + 1 Multipliers," *IET Computers and Digital Techniques*, Vol. 1, No. 1, pp. 49-57, January 2007.

[Veer07] Veeramachaneni, S., K. Krishna M, L. Avinash, S. R. Puppala, and M.B. Srinivas, "Novel Architectures for High-Speed and Low-Power 3-2, 4-2 and 5-2 Compressors," *Proc. 20th Int'l Conf. VLSI Design*, pp.324-329, 2007. **Authors' Reponses to Reviewers' Comments**

Reviewer comments appear in italics.

Reviewer 1: Comments to the Author

It would be better if the last section of the paper is augmented with discussions on real

savings in terms of number of gates when the proposed posibits/negibits numbering

systems is used. A final table with comparison results with alternative approaches in

terms of latency, number of gates and other comaprison parameters will make this

paper much better.

The first sentence of the last paragraph of the introduction of this revised version, which

reads "In this paper, we aim to promote the use of WBS and inverted encoding of negabits

(IEN) in the design of digital arithmetic circuits.", and the following final paragraph, of the

conclusion section should adequately address the above concerns.]

"Our discussion in this paper has been qualitative, pointing to advantages in terms

of easier exploration of design space, simpler conceptual design (thus, design time

reduction and error avoidance), and use of highly optimized standard cells that are

available in the literature and in various design libraries. The use of standard arithmetic

building blocks allows our designs to benefit from the continuous innovations that lead

to faster, more compact, and lower-power components such as half-adders, full-adders,

and bit compressors. Quantitative assessments of the benefits would be possible only

for specific applications, after full circuit-level implementation. We have not done this in

the current paper, but instead refer the reader to our previous publications, cited in the

references, which do offer quantitative evaluations and comparisons."

Reviewer 2: Comments to the Author

There is a similar article with the same words with the following topic:

Posibits, Negabits, and Their Mixed Use in Efficient Realization of Arithmetic Algorithms from the same authors.

I wonder why there is no difference between the abstracts and conclusion parts They also did not reference their own previous article neither.

This paper is an extension of our conference paper, which is now included in the reference list. The following represented the 30% (7 pages out of 21) added material in our original submission:

Example 2 on pages 7-8: 1 page

Fig. 12 and the preceding paragraph on pages 13: 0.5 page

Example 7 on pages 14-15: 1.5 pages

Example 8 on pages 16-19: 4 pages

Moreover, the current revised version contains even more new material as new Fig. 12 and modified and added text in:

Abstract

Last Paragraph of the Introduction

Examples 1, and 3

Two new paragraphs at the outset of Section 3

Two new paragraphs at the outset of Section 4

Two new paragraphs in the middle and end of the conclusion section

Reviewer 3: Comments to the Author

In addition to some typos (such as "r efers" in Example 4, Position weights

misalignment below Fig. 1.e, different dot size in 9th line of Fig.5.b etc.),

These errors have been fixed.

the paper lacks from solid theoretical study on the use of proposed encoding or

description.

All of the needed theoretical background can be found in references [Jabe01],

[Jabe02], [Jabe05], [Jabe08], [Jabe10], and [Gorg11]. One aim of the present paper is

to gather in one place and weave together information from these and other sources for

the benefit of digital designers.

Said differently, though several examples are given, the designer does not know

how and when to use such encoding (mixed use of posibits and negabits).

A 3-step design flow has been added to the conclusion section to recap our

proposed methodology.

Moreover, though authors "self cite" frequently, they have missed to cite their

previous work indexed by IEEE Explore (Digital Object Identifier:

10.1109/CADS.2010.5623646 ) and present the novelty of this paper to it.

The required reference has been added (see our response to Reviewer 2).